Virtual Memory

CPU와 Main Memory사이에 cache가 있는 것과 같이 Secondary disk storage를 Main Memory의 cache로 사용한다.

processor가 사용하는 주소공간과 컴퓨터에 설치된 memory가 제공하는 주소공간을 분리하는 것

- 실제 program을 실행하려면 memory에 적재되어야한다.

- 하지만 대부분의 program은 전체가 동시에 실행되지 않고 지역성이 있기 때문에 부분적으로 memory에 적재해서 사용한다.

- program의 일부만 memory에 적재하고 나머지는 secandary stroge에 적재해서 실제 주소공간 보다 더 큰 주소 공간을 프로세스에 제공할 수 있다.

- CPU와 OS에 의해 관리된다. (이 과정을) - > MMU(Memory Management Unit), translation table, page descriptor

: 가상 주소를 물리 주소로 transalte, conversion

: memory protection & sharing

: 효율적인 memory 사용

- 프로그래머는 메모리 관리에 대해 자유롭다. regardless

동작

- VM의 이동 단위 block을 page라고한다.

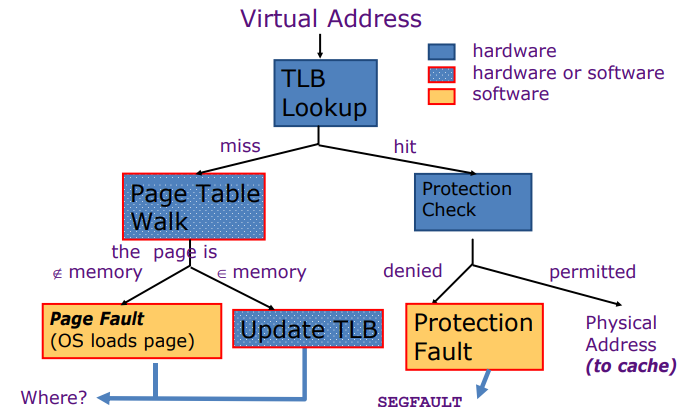

- VM에서 miss가 발생하면 page fault라고 한다.

- VM의 크기는 CPU addressing capability에 의해 결정된다.

- CPU가 physical memory의 program과 data를 참조하는 것은 memory에 있는 secondary storage의 복사본을 참조하는 것이다. // physical memory는 무시한다.

- 즉 memory에 복사본이 있다면 메모리에서 CPU로 가져와서 사용하고, memory에 복사본이 없다면 secondary storgae에 있는 원본을 memory에 복제한 후 동일한 방법으로 사용하면 된다.

- 여러 program이 공통된 library를 사용한다면, 하나만 main memory에 있고 동시에 sharing한다.

USAGES

- physical memory 초과하는 program

- Multi-programming

- System independent application program

- System development independent on physical memory

Translation table

virtual pages로 부터 구성된다.

valid bit, 해당하는 physical page

Operation

- processor의 가상 주소로 부터 가상 page 번호를 얻는다

: 가상 주소 - virtual page number | page 내 offset

: 물리 주소 - physical page number | page 내 offset

- virtual page number로 page table 접근

: main mermory에 있으면 physical memory address를 가지고 접근.

: 없으면 virtual address에 해당하는 것을 physical memory에 가져다 놓고 재접근.

Virtual Memory Application

main memory를 공유한다.

-각자의 code와 data가 vm에 있다. (노,보,초)

- 서로를 보호한다. 침범하지 않는다.

- 각 사용자는 page table을 가진다. (흰)

physical memory에 관계없는 system개발

- system program은 physical memory address 0부터 실행하도록 설계

- system이 physical or designed memory layout으로 load됨

- addresss translation으로 program에 접근

- 프로그램이 다른 시스템으로 이식 된 경우에만 변환을 변경??

page table을 사용하면 program의 page를 비연속적으로 저장할 수 있습니다.

Paging Organization

- page transferring 은 Disk에 access해야하므로 비용이 크다.

: 큰 miss penalty를 발생한다. 그래서 page를 상당히 크게 만들어야한다. (4Kib)

: page fault를 줄이는게 중요하다 (LRU는 가격 대비 가치가 있다)

: Write-through은 비용이 커서 Write-back을 사용

page는 main memory에 있음

** 이해부족

page size 12bit가 된 기준이 뭐임 ?

Basic Page Address Translation

VPN(Virture Page Number)의 bit수 만큼 page table(PT)있음

PT size는 VPN 비트 수 * physical address bit 크기 만큼

2^20 * 24 = 24 Mibits =3Mibits*8= 3MiB per user // Page Table 크기

virtual addresss space가 64bit이면 2^44개의 PTE(Page Table Entry, 한줄!)이 있다.

2*44 * 24

기본 주소 변환 방법 page table 방식

- paging 기법은 physical memory와 virtual memory를 page단위로 분할한다.

- main memory의 page를 frame이라고 한다.

- table을 이용하여 translation한다.

- PTR(Page Table Register)가 지시한다.

- processor가 전환될 때 PRT은 page table을 가리킨다.

- PTE(Page Table Entry)는 PPN(physical page number)과 제어부분(Access Protection + V)

- table내 page entry 위치는 VPN. 이걸 PTR이 가리킴

- 여기서 V확인하고 0이면 없으니깐 CPU에 "Secondary Stroge의 page를 Memory로 전송하고 PTE갱신하라고" 요청

- 있으면 Access Protection(접근권한) 확인하고 권한이 없으면 CPU에 signal전송, 있으면 PTE로부터 PPN필드를 읽는다.

- 읽은 PPN과 virtual address를 합쳐서 실제 주소 생성.

Two-Level Paging System

Table의 크기가 쓸데 없이 너무 크다. 보통 program이 그렇게 크지 않다.

그래서 table을 분리한다. 10bit에 해당하는 table1, table2

실제사용하는 것만 연결해서 사용한다. 용량 낭비x

단점 실제 Main Memory에 access하기 위해서 table들이 있는 main memory에 3번 access한다.

Fast Translation Using a TLB

TLB(Translation Look-aside Buffer)

page table을 access하는데 특별한 cache를 만든다.

page table에서 자주 access하는 부분만 caching할 수 있는 hardware를 만든다.

CPU 내에서 빠른 PTE cache인 TLB (Translation Look-aside Buffer)을 사용한다.

CPU가 virtual address발생시키고 page table에 접근하기 전에 TLB에 access하고 정보가 있으면 physical address 생성해서 바로 접근

Typical

- 16 ~ 512 PTEs

- 0.5 ~ 1 cycle for hit

- 10 ~100 cycles for miss

- 0.01% ~ 0.1% miss rate

Miss는 softwore 또는 hardware로 처리할 수 있다.

cache의 tag로 physical address를 사용하면 cache를 보기전에 translate 해야하므로 virtual address를 사용한다.

/*– Complications due to aliasing

• Different virtual addresses for shared physical address

– 앨리어싱으로 인한 복잡

• 공유 물리적 주소에 대한 다른 가상 주소*/ 뭐라는겨 ,.

'컴퓨터 구조' 카테고리의 다른 글

| 컴퓨터 구조 14장 - Input / Output (0) | 2020.06.17 |

|---|---|

| 컴퓨터 구조 13장 - Parallel Processor (0) | 2020.06.17 |

| 컴퓨터구조 12장 - Memory 2 : Associative Caches (1) | 2020.06.17 |

| 컴퓨터 구조 11장 - Memory 1 (0) | 2020.06.16 |

| 컴퓨터 구조 7장 - Processor (2) | 2020.05.12 |