버스 시스템 개요

• Bus개념의 시작

– system내의 모듈에 공유되는 전기적 신호선

• 모듈이 연결될 수 있는 여러 연결점을 가짐

• 같은 특성의 병렬 전기적 와이어로 구성

• 한 순간에 하나의 병렬 신호만 사용 모두 공유하고 있기 때문에

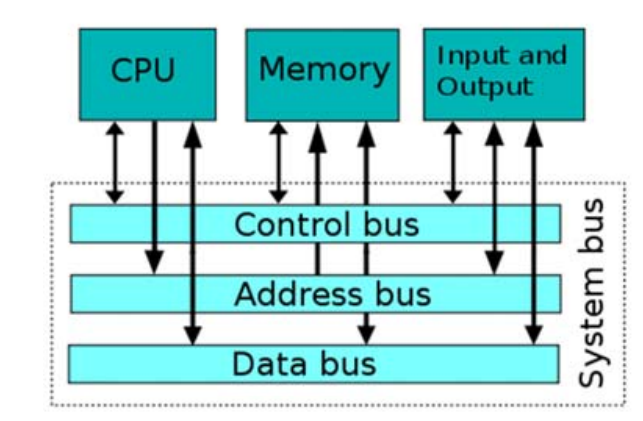

• Data Bus, Address Bus, Control Bus

– 모듈 사이의 병렬 데이터 전송을 공유 Bus 규약

• 공통 특성의 선들로 구성된 Bus들의 집합

• Bus 사양: 물리적 레이어부터 트랜잭션 프로토콜까지

• 최근의 Bus 정의

– system내외부 모듈 사이에 데이터 전송을 위한 공유되는 통신 링크 규약

• 병렬 또는 직렬 연결(ex USB)

• 멀티드롭(Multidrop), 데이지 체인, 스위치드 허브 연결

• 시스템 내부 모듈 연결 또는 외부장치 연결

– 네트워크 프로토콜과 경계가 흐리지고 있음

• 이더넷(이와 유사하게 특성으로 구성되어 있다)

• 버스 사양

– 선들의 전기적 규격

– 선들의 길이, 저항과 커넥터의 형태와 같은 물리적/기계적 특징

– 클럭과 신호들의 타이밍

– 버스 요청및 승인, 명령의 전달, 데이터의 전송과 같은 트랜잭션

• PC 버스의 예

- 1981년: ISA 버스

- 1984년: IBM AT 버스

- 1988년: EISA 버스

- 1992년 VESA 버스 그래픽 처리하는 모니터의 등장으로 빠르게 데이터를 전송

- 1992년 ~ 2002년: PCI 버스, PCI-X 병렬연결 Bus

- 1997년: AGP 많은 Data를 전송하기 위해

- 2003 PCIe 1.0 Serial Bus

- 2010 PCIe 3.0

- 2017 PCIe 4.0

• 장점

– 새로운 장치가 쉽게 연결이 된다.

– 표준 버스 규격의 장치는 다양한 시스템에 자유롭게 연결된다.

– 시스템 연결 비용이 적다.

• 단점

공유자원이다.

– 통신 병목 현상을 발생시킨다.

• 대역폭이 최대 입출력 성능을 제한한다.

• 최대 버스 속도의 제한 요소

– 버스의 길이

– 버스상의 장치의 수

– 지원하는 다양한 장치 형태

• 다양한 지연 시간

• 다양한 데이터 전송 속도

Bus Signal and Communication Protocols

Control : data 전송방향, data 크기, bus제어 등 해결

Address : CPU, DMAS가 보내는 주소

Data : Data~

synchronus

clock에 의해 동기되어서 data전송이 이루어진다.

clock 1이라는 시간에 address가 available하다 그래서 address를 읽으면 data를 읽는다. 5clock에 data읽었네

data전송해야 돼~ 1

주소보내 2

ack 받으면 ㅇ

ack신호 받으면서 왔다리갔다리

마스터 (Master)와 슬레이브(Slave) // 대표적으로 CPU와 MEMORY

• 버스 트랜잭션(처리? 거래?)은 두 부분으로 구성된다.

– 요청(대표적으로 CPU) <- 마스터의 명령

– 데이터의 전송 -> 동작

:요청에 의해 수동적으로 Memory가 동작을 한다 전송

• 마스터는 버스 트랜잭션을 시작한다.

– 주소와 명령어를 보냄으로써 트랜잭션을 시작

• 슬레이브는 명령에 따라 반응한다.

– 마스터가 데이터를 요청하면 데이터를 보낸다.

– 마스터가 데이터를 보내면 데이터를 받는다.

• 간단한 시스템

– 프로세서가 버스에서의 유일한 마스터

– 모든 버스 트랙잭션을 프로세서가 관장

– 단점: 프로세서가 모든 트랜잭션에 관여 (입출력 경우 CPU부담, 그래서 DMAC가 마스터가 됨)

다수 마스터와 버스 중재 (Bus Arbitration)

• 버스 중재

– 다수의 마스터가 있을 경우에 공유 자원인 버스의 사용을 조정

• 버스 중재 동작

– 버스를 사용하고자 하는 마스터는 버스를 요청 (bus request)

• 버스 마스터는 요청을 승인받기 전까지 버스를 사용하지 못한다.

– 버스 중재 하드웨어는 버스 사용 마스터를 선정하고 통보 (bus arbitor)

– 버스 마스터는 버스의 사용이 끝났을 경우에 이를 공지

• 버스 중재는 다음 두 요소를 조화시켜야 한다.

– 버스 우선순위: 높은 우선 순위의 장치가 먼저 서비스 받는다.

– 공정성: 가장 낮은 우선순위 장치라도 언젠가는 버스를 사용할 수 있어야 한다.

• 버스 중재 스킴

– 데이지 체인 중재 (Daisy Chain Arbitration)

– 중앙 병렬 중재 (Centralized Parallel Arbitration)

– 충돌에 기반한 분산 중재 (Distributed Arbitration by Collision)

Daisy Chain Arbitration

여러 마스터를 chain형태로 연결시키는 것

Request, Release : wired OR

• 동작

– 장치들이 버스 요청을 하면 버스조정자는 Release 선을 통해 버스의 사용여부를 확인하고 아무도 사용하지 않으면 Grant signal를 첫번째 장치에 1을 보낸다.

– 최고순위 장치가 버스를 사용하지 않으면 다음 장치로 Grant를 보낸다. 옆으로 전달

– 버스를 사용할 장치는 Release를 1로하고 버스를 사용한다.

• 장점

– 우선순위가 연결 구성에 의해 결정되며 간단하다.

중재기의 가장 가까운 것이 우선 순위가 높다

• 단점

– 공정성을 보장하지 않는다.

• 낮은 우선 순위 장치는 무한적으로 버스를 사용 못할 수 있다.

• 체인 형태의 그랜트 신호선은 버스의 속도를 늦춘다.

버스의 사용할 빈도가 높지 않을 경우에만 쓴다.

Centralized Parallel Arbitration

중앙 병렬 조정방식

• 동작

– 버스를 사용하고자 하는 마스터는 버스 중재기에게 요청한다.

– 버스 중재기는 마스터 요청들을 기반으로 선정 알고리즘을 수행하여 선정된 장치에게 Grant를 보낸다.

Grant, Request를 각자 가지고 있어서 누구 쓰고싶은지 알 수 있다.

• 특성

– 버스 중재기는 버스를 요청한 마스터와 허용한 마스터를 알고 있음

– 버스조정자의 구현에 따라 다양한 선택 알고리즘이 가능

• 대부분의 프로세서-메모리 버스와 고성능 입출력 버스에서 사용

가장 많이 씀

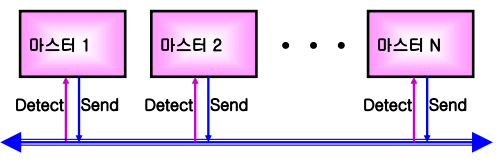

Distributed Arbitration with Collision

충돌에 의한 분산 조정 방식

• 동작

– 버스를 사용할 마스터는 버스를 살펴보고 아무도 사용하지 않으면 목적지 주소를 가지는 데이터를 버스에 보내고 각 슬레이브는 주소를 검사하며 해당 슬레이브는 버스 동작 참여를 통보한다.

– 만약 두 개의 이상의 마스터가 동시에 데이터를 보내면 이는 버스 상에서 충돌이 되며 전송하는 마스터는 이를 확인하여 전송을 취소한다. (내가 보낸 것이 아닌 것이 흘러다닐 때 동시에 정지, 그리고 아래)

– 무작위 시간 뒤에 각 마스터는 전송을 다시 시도한다.

• 특징

– 중앙집중식의 버스 중재기가 없이 각 마스터들이 버스의 상태만 확인하여 분산적으로 중재가 일어난다.

• Ethernet에서 사용하며 맥 시스템에서 비슷한 방식을 사용

CSMA/CD

AMBA (Advanced Microcontroller Bus Architecture)

• 칩 내의 모듈들은 연결하기 위한 버스 규약 <- ARM

– 계층적 버스 아키텍처

• AMBA 2.0의 3가지 버스

– AHB (Advanced High-Performance Bus)

• 고성능 시스템 백본 버스

– 파이프라인, 다중 마스터

– 버스트, 분리 트랜잭션

– ASB (Advanced System Bus)

• AHB 부분집합

– 파이프라인, 다중 마스터

– APB (Advanced Peripheral Bus)

• 저전력 주변 장치 버스

• 간단한 인터페이스

• AMBA 3.0 AXI

– 단방향 채널

– 다중 트랜잭션, 순서바뀜 완료

– 개선된 읽기 쓰기

현재 4.0까지 나옴

'컴퓨터 구조' 카테고리의 다른 글

| 컴퓨터 구조 8장 - FP (0) | 2020.06.20 |

|---|---|

| 컴퓨터 구조 14장 - Input / Output (0) | 2020.06.17 |

| 컴퓨터 구조 13장 - Parallel Processor (0) | 2020.06.17 |

| 컴퓨터구조 12장 - Memory 2 : Virtual Memory (0) | 2020.06.17 |

| 컴퓨터구조 12장 - Memory 2 : Associative Caches (1) | 2020.06.17 |